## INTEGRATED CIRCUITS

# DATA SHEET

# P87CL888 80C51 Ultra Low Power (ULP) telephony controller

Product specification Supersedes data of 2000 Sep 25 2002 Apr 24

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

| CONTE                                      | NTS                                                                                                                                                        | 9                            | APPLICATION INFORMATION                                                                           |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------|

| 1 2                                        | FEATURES GENERAL DESCRIPTION                                                                                                                               | 9.1<br>9.2                   | Introduction Differences between P87CL888 and the Metalink EH emulation system                    |

| 3<br>4                                     | ORDERING INFORMATION BLOCK DIAGRAM                                                                                                                         | 9.3<br>9.4                   | The asynchronous handshake CPU Telecom applications                                               |

| 5                                          | PINNING INFORMATION                                                                                                                                        | 10                           | HOW TO ESTIMATE P87CL888 POWER CONSUMPTION                                                        |

| 5.1<br>5.2<br>6                            | Pin configuration Pin description FUNCTIONAL DESCRIPTION                                                                                                   | 10.1<br>10.2<br>10.3         | General Modes Examples of power consumption estimation                                            |

| 6.1<br>6.2                                 | Oscillator circuitry The CPU                                                                                                                               | 11<br>12                     | LIMITING VALUES CHARACTERISTICS                                                                   |

| 6.3<br>6.4<br>6.5                          | Interrupt controller Key Pad Interrupt (KPI) Port control logic                                                                                            | 13                           | ELECTRICAL SPECIFICATION FOR DEVICE PROGRAMMING                                                   |

| 6.6                                        | Timer 0 and Timer 1 event counters                                                                                                                         | 14                           | PACKAGE OUTLINE                                                                                   |

| 6.7<br>6.8                                 | Timer 2                                                                                                                                                    | 15                           | SOLDERING                                                                                         |

| 6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13 | Watchdog Timer I <sup>2</sup> C-bus serial I/O (master/slave interface) MSK modem AD/DA converter Internal Data Memory Special Function Registers Overview | 15.1<br>15.2<br>15.3<br>15.4 | Introduction to soldering surface mount packages Reflow soldering Wave soldering Manual soldering |

| 7                                          | GENERAL DESCRIPTION OF DEVICE PROGRAMMING                                                                                                                  | 15.5                         | Suitability of surface mount IC packages for wave and reflow soldering methods                    |

| 7.1                                        | Introduction                                                                                                                                               | 16                           | DATA SHEET STATUS                                                                                 |

| 7.2                                        | SFRs for device programming                                                                                                                                | 17                           | DEFINITIONS                                                                                       |

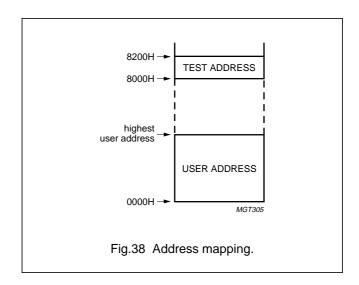

| 7.3                                        | Address space mapping                                                                                                                                      | 18                           | DISCLAIMERS                                                                                       |

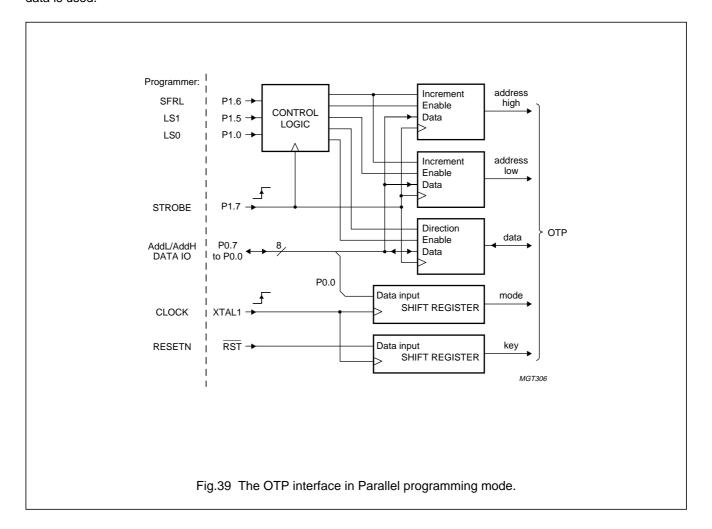

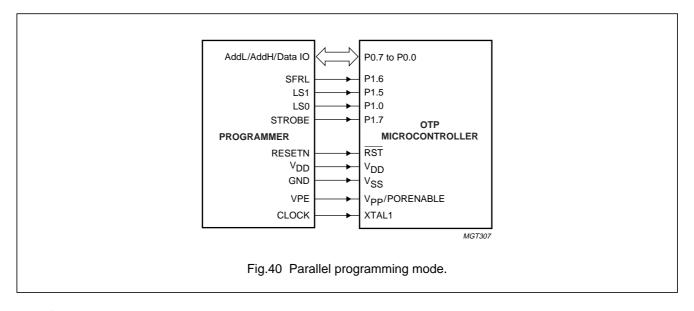

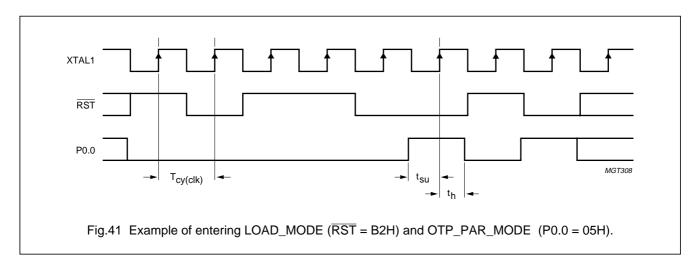

| 7.4<br>7.5                                 | The Parallel programming mode<br>In-system programming                                                                                                     | 19                           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                                   |

| 8                                          | INSTRUCTION SET                                                                                                                                            |                              |                                                                                                   |

| 8 1                                        | Instruction man                                                                                                                                            |                              |                                                                                                   |

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 1 FEATURES

- Full static asynchronous handshake 80C51 CPU; enhanced 8-bit architecture with:

- Standard 80C51 instruction set

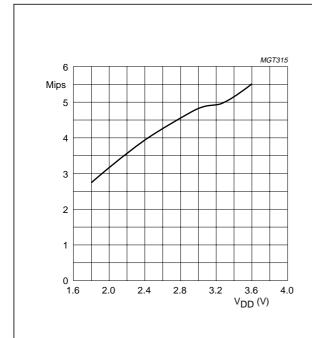

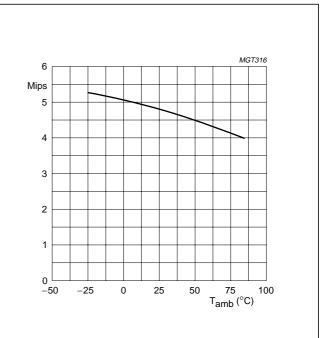

- CPU speed independent of clock frequency, average speed: 4.8 Mips at 3.0 V

- Non-page oriented instructions

- Direct addressing

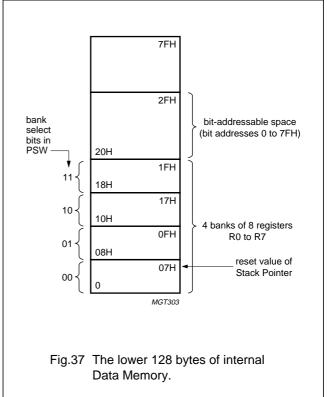

- Four 8-byte RAM register banks

- Stack depth limited only by available internal RAM (maximum 256 bytes)

- Multiply, divide, subtract and compare instructions.

- Twenty source, twenty vector interrupt structure with two priority levels, polarity and sensitivity choice

- · Key pad interrupt:

- Edge or level sensitive triggering selectable via software

- Enabling low-power and low-EMI keyboard control.

- 32 general purpose I/O pins

- Timer 0 and Timer 1: two standard 16-bit timer/event counters

- Timer 2: 16-bit timer/event counter with capture, compare and auto-reload function

- Watchdog Timer

- · Wake-up counter

- Idle and Power-down mode

- 8-kbyte blank One Time Programmable (OTP) memory or factory programmed OTP memory

- In-system programming of OTP memory

- Supply voltage: 1.8 to 3.6 V

- 256 bytes RAM

- · Internal crystal oscillator

- · Power-on reset circuitry with disable pin

- · Reset I/O pin for external reset from master or to slave

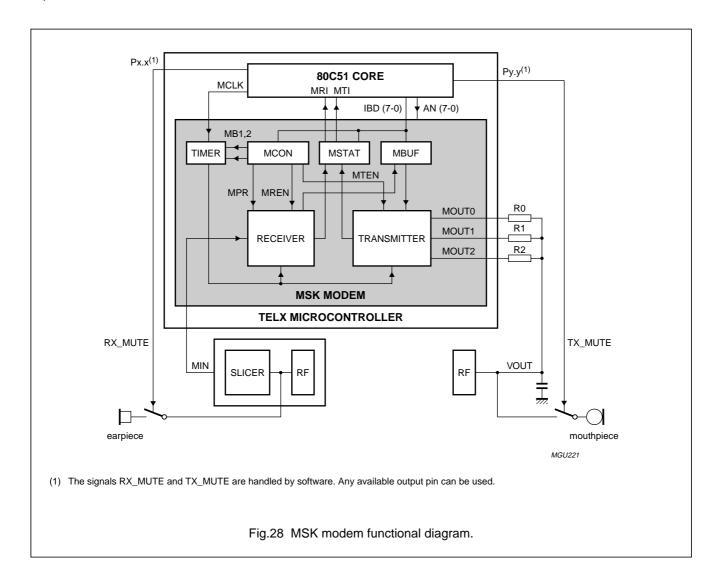

- MSK modem including Manchester encoder/decoder with 2 digital outputs (by SW) for analog cordless telephones (standards CT0/CT1/CT1+)

- I<sup>2</sup>C-bus master/slave (transmitter/receiver, maximum frequency 400 kHz)

- 8 bit digital-to-analog converter with two different outputs

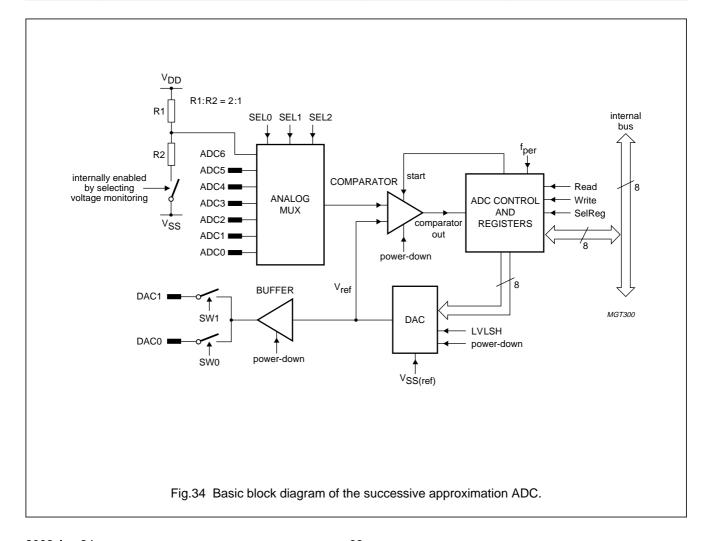

- 6 inputs Comparator with input multiplexer (for successive approximation analog-to-digital conversion).

#### 2 GENERAL DESCRIPTION

The P87CL888 is manufactured in an advanced CMOS technology. The P87CL888 is a member of the VTELX microcontroller family which is a low-power family of low-voltage 80CL51 microcontrollers with advanced features for telecom applications. The Philips exclusive, asynchronous handshaking technology has been used for the CPU implementation which makes the CPU to run at its maximum speed independent of the used crystal frequency.

The P87CL888 is especially suited for low cost analog cordless telephone applications (CT0, CT1 and CT1+ standards) and wired feature phones. For this purpose, functions like ADC/DAC, MSK modem, I<sup>2</sup>C-bus and key interrupts are integrated on-chip.

The device is optimized for low power consumption. It has two software selectable modes for power reduction: Idle and Power-down. In addition, the clock to all unused peripheral blocks can be switched off.

The instruction set is based on that of the 80C51. The P87CL888 also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 46 two-byte, and 16 three-byte. Due to the missing Port P2, there is no external data or memory access and the MOVX operations cannot be used.

2002 Apr 24

3

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 3 ORDERING INFORMATION

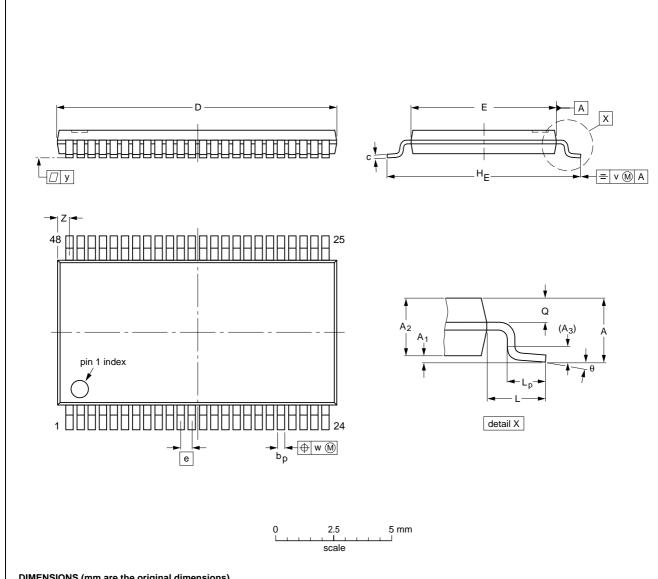

| TYPE NUMBER                                                  | PACKAGE |                                                                        |          |  |  |

|--------------------------------------------------------------|---------|------------------------------------------------------------------------|----------|--|--|

| I I PE NOWIBER                                               | NAME    | DESCRIPTION                                                            | VERSION  |  |  |

| P87CL888T/000 <sup>(1)</sup><br>P87CL888T/xxx <sup>(2)</sup> | TSSOP48 | plastic thin shrink small outline package; 48 leads; body width 6.1 mm | SOT362-1 |  |  |

#### Notes

- 1. Blank OTP.

- 2. Factory-programmed OTP.

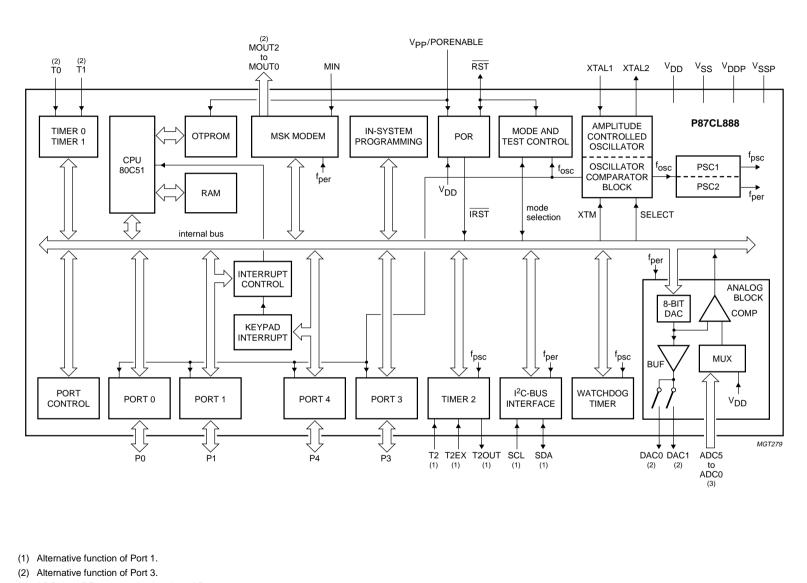

**BLOCK DIAGRAM**

Philips Semiconductors

(3) ADC3 to ADC5: alternative function of Port 1; ADC0 to ADC2: alternative function of Port 3.

Fig.1 Simplified block diagram.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

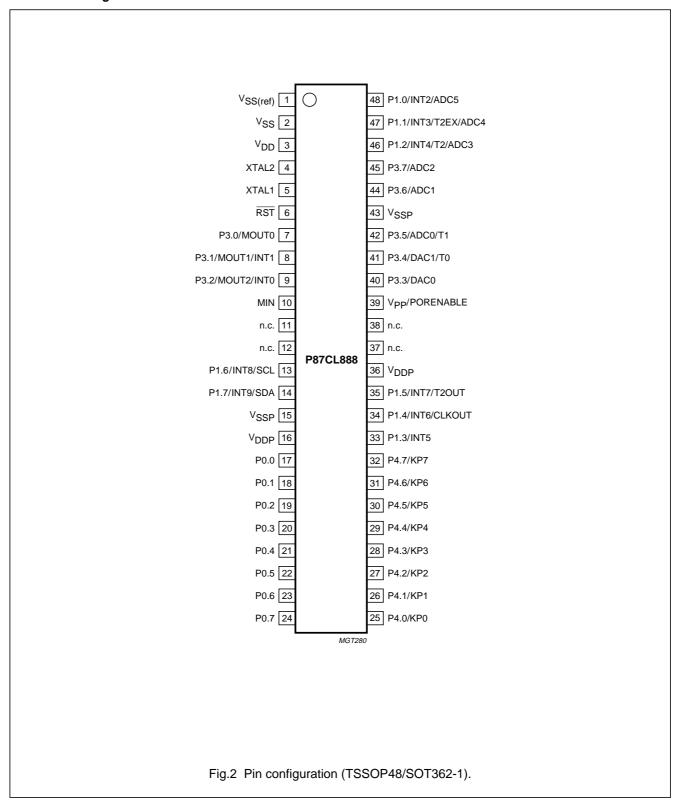

#### **5 PINNING INFORMATION**

#### 5.1 Pin configuration

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

### 5.2 Pin description

Table 1 Pin description for TSSOP48 (SOT362-1)

| SYMBOL                          | PIN      | TYPE | DESCRIPTION                                                                                                                                                                                                |  |  |

|---------------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>SS(ref)</sub>            | 1        | S    | negative reference supply voltage (for bandgap)                                                                                                                                                            |  |  |

| V <sub>SS</sub> <sup>(1)</sup>  | 2        | S    | ground                                                                                                                                                                                                     |  |  |

| V <sub>DD</sub> <sup>(1)</sup>  | 3        | S    | power supply                                                                                                                                                                                               |  |  |

| XTAL2                           | 4        | 0    | crystal output                                                                                                                                                                                             |  |  |

| XTAL1                           | 5        | I    | crystal input; external clock input                                                                                                                                                                        |  |  |

| RST                             | 6        | I/O  | reset input/output pin; active LOW                                                                                                                                                                         |  |  |

| P3.0/MOUT0                      | 7        | I/O  | Port 3: P3.0 to P3.2; bidirectional I/O port with alternative functions                                                                                                                                    |  |  |

| P3.1/MOUT1/INT1                 | 8        | I/O  | MOUT2 to MOUT0: MSK outputs (mapped on the lower 3 bits of Port 3).                                                                                                                                        |  |  |

| P3.2/MOUT2/INT0                 | 9        | I/O  | P3.2 also serves as the external interrupt 0 input (INT1) and P3.1 as the external interrupt 1 input (INT0).                                                                                               |  |  |

| MIN                             | 10       | I    | MSK input                                                                                                                                                                                                  |  |  |

| n.c.                            | 11, 12   | 1    | not connected                                                                                                                                                                                              |  |  |

| P1.6/INT8/SCL                   | 13       | I/O  | Port 1: P1.6 and P1.7; can only be used as open-drain output or                                                                                                                                            |  |  |

| P1.7/INT9/SDA                   | 14       | I/O  | high-impedance input. Alternative functions: INT8 and INT9, external interrupt 8 and 9. SCL and SDA I <sup>2</sup> C-bus interface clock and data.                                                         |  |  |

| V <sub>SSP</sub> <sup>(1)</sup> | 15, 43   | S    | periphery (I/O) ground                                                                                                                                                                                     |  |  |

| V <sub>DDP</sub> <sup>(1)</sup> | 16, 36   | S    | periphery (I/O) positive supply voltage                                                                                                                                                                    |  |  |

| P0.0 to P0.7                    | 17 to 24 | I/O  |                                                                                                                                                                                                            |  |  |

| P4.0/KP0 to P4.7/KP7            | 25 to 32 | I/O  | Port 4: 8-bit bidirectional I/O port with multiplexed alternative functions Key Pad Interrupts: KP0 to KP7. Every port can be used as open-drain, standard port, high-impedance input or push-pull output. |  |  |

| P1.3/INT5                       | 33       | I/O  | Port 1: P1.3 to P1.5; bidirectional I/O port with alternative functions INT5,                                                                                                                              |  |  |

| P1.4/INT6/CLKOUT                | 34       | I/O  | INT6 and INT7: external interrupt 5 to 7. P1.4 also serves as auxiliary                                                                                                                                    |  |  |

| P1.5/INT7/T2OUT                 | 35       | I/O  | clock output (CLKOUT). P1.5 also serves as the Timer 2 output (T2OUT).                                                                                                                                     |  |  |

| n.c.                            | 37, 38   | _    | not connected                                                                                                                                                                                              |  |  |

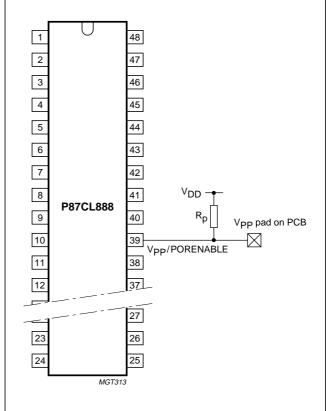

| V <sub>PP</sub> /PORENABLE      | 39       | S    | high voltage input pin for OTP programming/power-on reset enable signal                                                                                                                                    |  |  |

| P3.3/DAC0                       | 40       | I/O  | Port 3: P3.3 to P3.5; bidirectional I/O port with alternative functions DAC0,                                                                                                                              |  |  |

| P3.4/DAC1/T0                    | 41       | I/O  | DAC1: DAC outputs and ADC0: ADC input 1. P3.4 also serves as the                                                                                                                                           |  |  |

| P3.5/ADC0/T1                    | 42       | I/O  | Timer 0 external count input (T0). P3.5 also serves as the Timer 1 external count input (T1).                                                                                                              |  |  |

| P3.6/ADC1                       | 44       | I/O  | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                                                                                                                                                                      |  |  |

| P3.7/ADC2                       | 45       | I/O  | ADC1 and ADC2: ADC inputs 1 and 2.                                                                                                                                                                         |  |  |

| P1.2/INT4/T2/ADC3               | 46       | I/O  | Port 1: P1.2 to P1.0; bidirectional I/O port with alternative functions INT4,                                                                                                                              |  |  |

| P1.1/INT3/T2EX/ADC4             | 47       | I/O  | INT3 and INT2: external interrupts 4, 3 and 2. P1.2 also serves as Timer 2                                                                                                                                 |  |  |

| P1.0/INT2/ADC5                  | 48       | I/O  | input (T2) or ADC input 3 (ADC3). P1.1 also serves as Timer 2 external input (T2EX) or ADC input 4 (ADC4). P1.0 also serves as ADC input 5 (ADC5).                                                         |  |  |

#### Note

1. For high current drive capability on I/Os all supply pins should be connected.

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### **6 FUNCTIONAL DESCRIPTION**

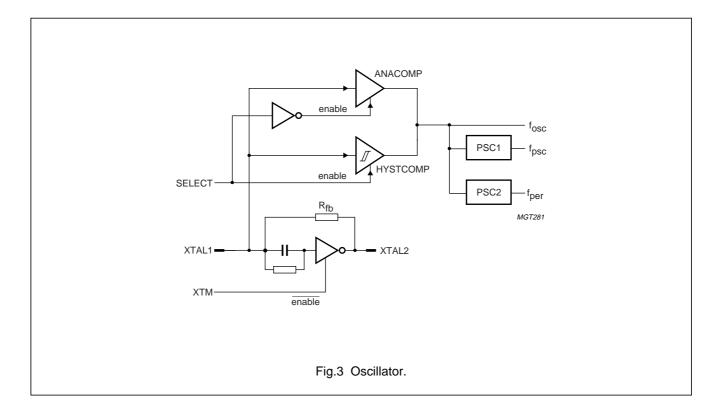

#### 6.1 Oscillator circuitry

The on-chip Amplitude Controlled Oscillator (ACO) circuitry is a single-stage inverting amplifier biased by an internal feedback resistor  $R_{fb}$ . The oscillator circuit is shown in Fig.3.

Two comparators with different characteristics can be used with the on-chip crystal oscillator. The first one is an analog comparator built around a differential amplifier and is intended to be selected when an external ceramic or crystal resonator is connected to the chip.

The other comparator has a Schmitt-trigger input with a bigger hysteresis which is especially useful when the P87CL888 is driven from an external clock source.

Two bits in the SYSCON SFR, SELECT and XTM, are used to configure the oscillator. The SELECT bit (SYSCON.1) enables the analog comparator or the hysteresis comparator.

With XTM (SYSCON.0) = 1 (or in Power-down mode; PCON.1 = 1) the oscillator is switched off and the current consumption of the oscillator is reduced to zero.

Table 2 Comparator select bits in SYSCON SFR

| SELECT | XTM | DESCRIPTION                                       |

|--------|-----|---------------------------------------------------|

| 0      | 0   | oscillator enabled; analog comparator enabled     |

| 0      | 1   | don't use                                         |

| 1      | 0   | oscillator enabled; hysteresis comparator enabled |

| 1      | 1   | oscillator stopped; hysteresis comparator enabled |

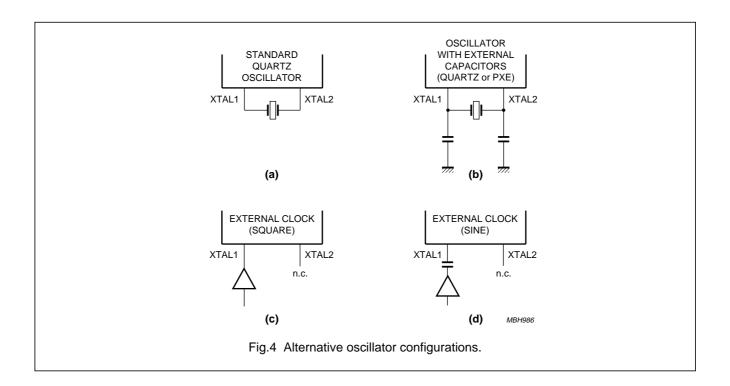

#### 6.1.1 CLOCK OSCILLATOR CONNECTIONS

No external components are needed, when a quartz crystal is used to drive the oscillator. When an external ceramic resonator is used to drive the oscillator, external components may be required depending upon the used ceramic resonator; refer to the product specification. Two different resonator configurations are shown in Figs 4a and 4b.

To drive the device with an external clock source, apply the external clock signal to XTAL1, and leave XTAL2 floating, as shown in Fig.4c. If the amplitude of the input signal is less than  $V_{DD}$  to  $V_{SS}$  or if a sine wave is applied, capacitive decoupling is needed as shown in Fig.4d.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

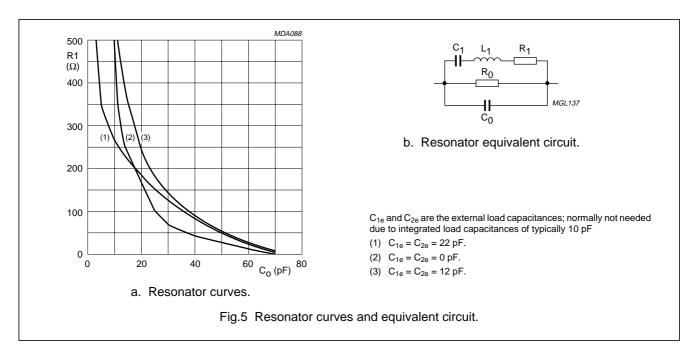

#### 6.1.2 RESONATOR REQUIREMENTS FOR THE ACO

For correct operation of the oscillator, the values of  $R_1$  and  $C_0$  of the chosen resonator (quartz or PXE) must be below the line shown in Fig.5a. The value of the parallel resistor  $R_0$  must be less than 47 k $\Omega$ . The wiring between chip and resonator should be kept as short as possible. Recommended resonator types are:

- CSA 3.58MG (supplier Murata)

- FCR3.58M5 (supplier TDK).

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.1.3 ON-CHIP CLOCKS

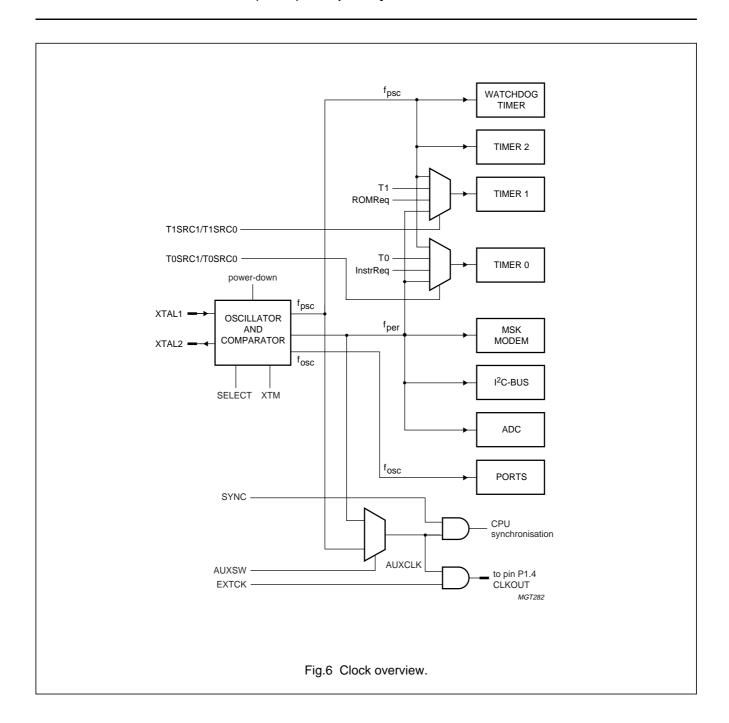

The microcontroller does not need a clock signal to run instructions, because the CPU is built using the Philips exclusive handshake technology. The peripheral blocks however are connected to a clock for synchronization with the outside world (e.g. MSK) or for a timed application (e.g. Timer 2). The block related SFRs (peripheral function) are therefore updated/modified with the applied clock. Two prescalers (PSC1 and PSC2) are implemented which allow the generation of two programmable clock signals  $f_{\text{psc}}$  and  $f_{\text{per}}$  for internal usage.

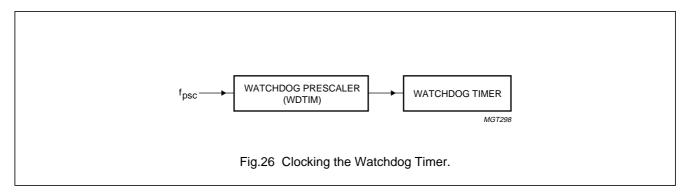

Signal  $f_{psc}$  from PSC1 is the default input clock of the timer blocks. The complete timer functionality is specified in the Section 6.6. Connected timers are the three 16-bit timers Timer 0, Timer 1 and Timer 2 and the 8-bit Watchdog Timer. The time interval of the connected timers can be adjusted by programming of PSC1. The output frequency  $f_{psc}$  can be changed by selecting the division factor with the bits PRESC.2, PRESC.1 and PRESC.0 (see Table 7).

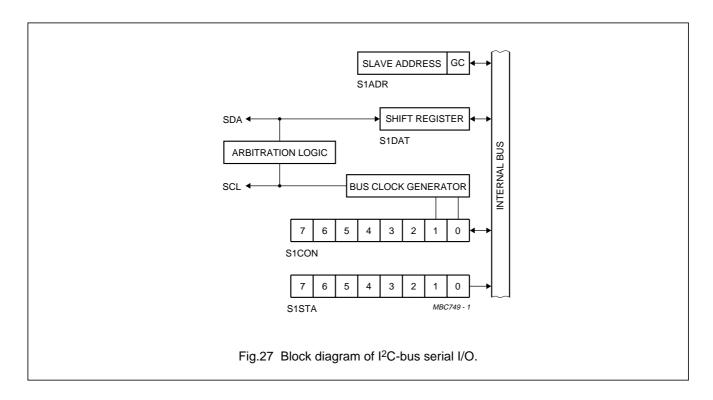

All peripheral blocks, which require a clock signal: MSK,  $I^2C$ -bus interface and ADC, are connected to the clock signal  $f_{per}$ . PSC2 can be programmed by setting bits PRESC.4 and PRESC.3 (see Table 7). The choice of the division factor must guarantee that all of the peripheral blocks are within their specification, specially if an external clock source of up to 12 MHz is applied.

Additionally Timer 1 and Timer 0 have a multiplexer on the clock input to choose from 4 different clock sources.

The multiplexers are switched by setting user controllable bits in the SYSCON SFR (bits 7 to 4). In the default setting both timers are incrementing on the clock signal  $f_{\rm psc}$  coming from PSC1. Timer 1 and Timer 0 can however also run on clock signal  $f_{\rm per}$  coming from PSC2. If used in the proper way this flexibility on the timer input sources can substantially contribute to a decrease in power consumption. Ideas and tips to reduce power consumption are given in Chapter 9.

The clock source of Timer 1 and Timer 0 can also be switched to an external clock input signal T1or T0 which are multiplexed with one of the device input pins.

This mode is also functional even when there is no system clock available. This means when a clock source is supplied on a port pin the Timer 1 or 0 can count and generate interrupts even when the chip is in Power-down mode. More details are specified in Section 6.6.

The last multiplexer input to the Timer 1 and Timer 0 is an auxiliary mode which can be used to obtain the operation speed from the handshake CPU. If this mode is activated for the Timer 1 input source, the timer increments on every ROM request. This means the timer increments by three for a three byte instruction and by two for a two byte instruction etc. If the auxiliary mode is activated for Timer 0 the timer increments on every instruction executed by the CPU. This means the timer register holds the number of instructions executed in a certain time frame. More ideas and tips how these clock source modes can be used together with the handshake CPU can be found in Chapter 9.

**Table 3** Timer 1 input source select modes Bits T1SRC[1:0] are defined in SYSCON SFR.

| T1SRC1 | T1SRC0                          | DESCRIPTION                                  |  |  |

|--------|---------------------------------|----------------------------------------------|--|--|

| 0      | 0                               | f <sub>psc</sub> is the Timer 1 clock input  |  |  |

| 0      | 1 T1 is the Timer 1 clock input |                                              |  |  |

| 1      | 0                               | the ROMreq signal is the Timer 1 clock input |  |  |

| 1      | 1                               | f <sub>per</sub> is the Timer 1 clock input  |  |  |

**Table 4** Timer 0 input source select modes Bits T0SRC[1:0] are defined in SYSCON SFR.

| T0SRC1 | T0SRC0 | DESCRIPTION                                    |

|--------|--------|------------------------------------------------|

| 0      | 0      | f <sub>psc</sub> is the Timer 0 clock input    |

| 0      | 1      | T0 is the Timer 0 clock input                  |

| 1      | 0      | the InstrReq signal is the Timer 0 clock input |

| 1      | 1      | f <sub>per</sub> is the Timer 0 clock input    |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.1.3.1 Prescaler Register (PRESC)

Reset value of PRESC SFR is XXX0 0000 (division factor 1 for PSC1 and PSC2).

**Table 5** Prescaler Register (SFR address F3H)

| 7     | 6     | 5    | 4       | 3       | 2       | 1       | 0       |

|-------|-------|------|---------|---------|---------|---------|---------|

| EXTCK | AUXSW | SYNC | PRESC.4 | PRESC.3 | PRESC.2 | PRESC.1 | PRESC.0 |

Table 6 Description of PRESC bits

| BIT    | SYMBOL      | DESCRIPTION                                                                                                      |

|--------|-------------|------------------------------------------------------------------------------------------------------------------|

| 7      | EXTCK       | switches AUXCLK to device pin P1.4 (CLKOUT)                                                                      |

| 6      | AUXSW       | Auxiliary Clock Switch; AUXSW = 0: AUXCLK equals f <sub>psc</sub> ;<br>AUXSW = 1: AUXCLK equals f <sub>per</sub> |

| 5      | SYNC        | switches the CPU to synchronous mode                                                                             |

| 4 to 0 | PRESC.[4:0] | these bits define the division factors for PSC1 and PSC2; see Table 7                                            |

Table 7 Division factors for PSC1 and PSC2

| DIVISION FACTOR                               |                                               |         |         |         |         |         |

|-----------------------------------------------|-----------------------------------------------|---------|---------|---------|---------|---------|

| PSC2<br>(f <sub>osc</sub> /f <sub>per</sub> ) | PSC1<br>(f <sub>osc</sub> /f <sub>psc</sub> ) | PRESC.4 | PRESC.3 | PRESC.2 | PRESC.1 | PRESC.0 |

| 1                                             | _                                             | 0       | 0       | X       | X       | X       |

| 2                                             | _                                             | 0       | 1       | Х       | Х       | Х       |

| 4                                             | _                                             | 1       | 0       | Х       | Х       | Х       |

| 8                                             | _                                             | 1       | 1       | Х       | Х       | Х       |

| _                                             | 1                                             | Х       | X       | 0       | 0       | 0       |

| _                                             | 2                                             | Х       | Х       | 0       | 0       | 1       |

| _                                             | 4                                             | Х       | Х       | 0       | 1       | 0       |

| _                                             | 6                                             | Х       | X       | 0       | 1       | 1       |

| _                                             | 8                                             | Х       | Х       | 1       | 0       | 0       |

| _                                             | 10                                            | Х       | Х       | 1       | 0       | 1       |

| _                                             | 12                                            | Х       | Х       | 1       | 1       | 0       |

| _                                             | 16                                            | X       | X       | 1       | 1       | 1       |

#### 6.1.4 AUXILIARY CLOCK SIGNAL MODES

The 3 most significant bits in the Prescaler Register (PRESC[7:5]; see Table 5 and 6) are used to enable additional clocking options. A multiplexer is implemented (see Fig.6) to choose between  $f_{psc}$  and  $f_{per}$  as source for AUXCLK. The multiplexer is operated by bit AUXSW (PRESC.6). With bit EXTCK (PRESC.7) the AUXCLK is fed to pin P1.4 (CLKOUT) for external use (initialize the port accordingly). Setting bit SYNC (PRESC.5) connects the AUXCLK to the instruction request input of the CPU. In this way the CPU is synchronised to the clock and an instruction is executed at every clock pulse of AUXCLK. In order to obtain exactly one instruction per clock cycle the period for AUXCLK must always be longer than the length of the slowest instruction.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

### 6.1.5 SYSTEM CONTROL REGISTER (SYSCON)

Table 8 System Control Register (SFR address B4H)

| 7      | 6      | 5      | 4      | 3 | 2 | 1      | 0   |

|--------|--------|--------|--------|---|---|--------|-----|

| T1SRC1 | T1SRC0 | T0SRC1 | T0SRC0 | _ | _ | SELECT | XTM |

Table 9 Description of SYSCON bits

| BIT | SYMBOL | DESCRIPTION                                                   |

|-----|--------|---------------------------------------------------------------|

| 7   | T1SRC1 | these 2 bits select the clock source for Timer 1; see Table 3 |

| 6   | T1SRC0 |                                                               |

| 5   | T0SRC1 | these 2 bits select the clock source for Timer 0; see Table 4 |

| 4   | T0SRC0 |                                                               |

| 3   | _      | do not use                                                    |

| 2   |        |                                                               |

| 1   | SELECT | comparator select bit; see Table 2                            |

| 0   | XTM    | oscillator disable bit; see Table 2                           |

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2 The CPU

#### 6.2.1 GENERAL

Ultra Low Power (ULP), points to the special 80C51 CPU architecture used in this device allowing significant power saving.

The CPU of the P87CL888 is realized in the Philips exclusive asynchronous handshaking technology, which is completely different to usual implementations of this core. The processor does not need a clock signal to run instructions. Every function within the CPU is self timed and always runs at the maximum speed that the silicon die under the current operating conditions allows (supply voltage and temperature). The advantage is the combination of a high computing power with reduced average power consumption and low EMC noise generation. Details about speed and energy consumption per instruction can be found in Chapter 8.

Summary of the CPU features:

- · No CPU clock is needed

- Only useful bytes are fetched from the program memory; the dummy read cycles which exist in the standard 80C51 have been eliminated to save power

- To further speed up the program execution; there is always a pre-fetch of the next byte of code from memory during the execution of the current instruction; in the case of a jump the pre-fetched byte is discarded

- In Idle mode the CPU power is reduced to leakage; only the enabled peripheral blocks consume power but can be switched off independently

- The only need for a clock is as a timing reference for timers/counters and to generate the timing for the I/O lines to synchronise with the off-chip world.

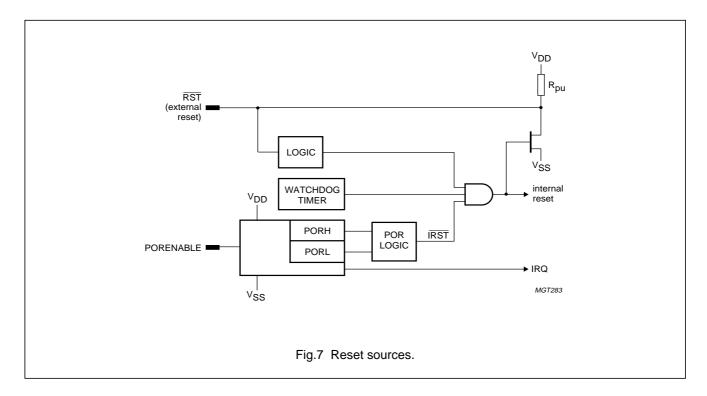

#### 6.2.2 RESET OPERATION

There are three possibilities to reset the CPU (see Fig.7):

- Power-On Reset (POR)

- · Watchdog Timer reset

- External reset via I/O pin RST.

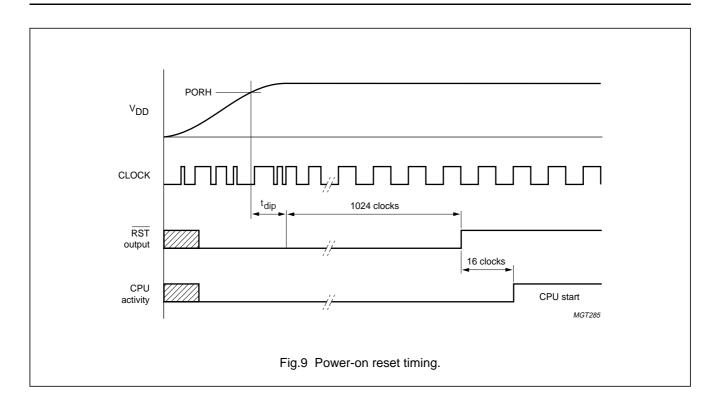

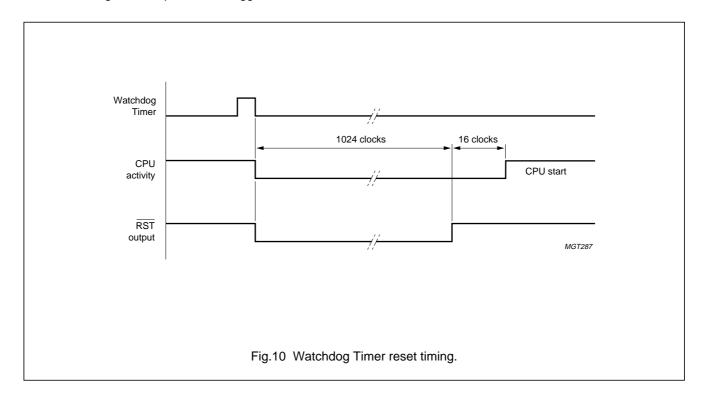

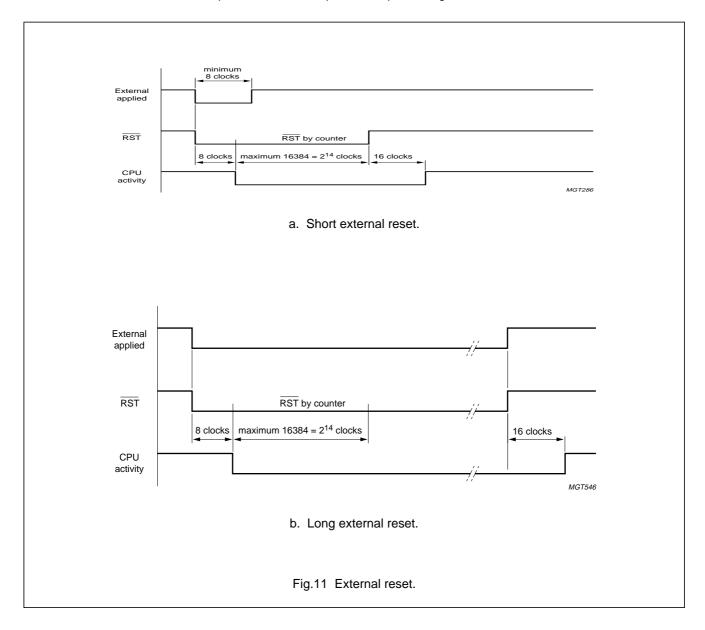

If an internal reset is executed (POR or Watchdog Timer), the reset pin  $\overline{RST}$  will be pulled to ground which can be used as reset signal for other ICs. The reset pin is LOW for at least 1024 clock cycles, and released 16 clock cycles prior to first code fetch (see Figs 9, 10 and 11).

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2.2.1 Power-On Reset (POR)

The device has an integrated power-on reset logic with a hysteresis between the two levels PORL and PORH. The value of PORL and PORH is chosen in such a way that a good start-up of the microcontroller is always guaranteed. If the transistor thresholds are high, caused by silicon processing, accordingly the POR levels will also be higher.

The power-on reset circuitry can be disabled by setting the input pin V<sub>PP</sub>/PORENABLE LOW. The IC must now be reset by applying a reset pulse to the  $\overline{RST}$  I/O pin. Note that not all device functionality is guaranteed for V<sub>DD</sub> voltages below PORL.

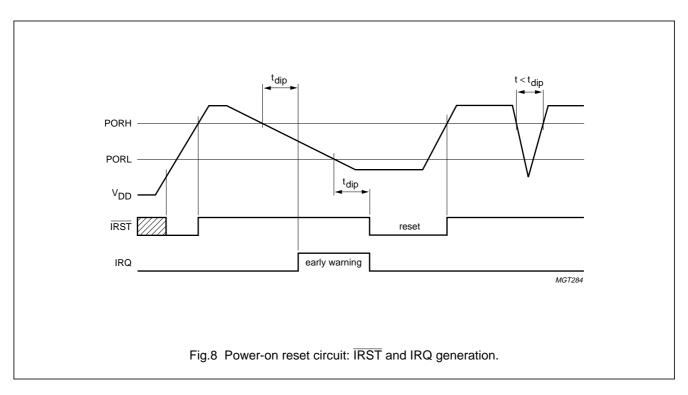

When  $V_{DD}$  falls below the level of PORH for longer then  $t_{dip}$  an 'Early Warning' interrupt signal IRQ is produced, and if  $V_{DD}$  falls below PORL for longer then  $t_{dip}$  an internal reset signal  $\overline{IRST}$  will be generated.

If the level crossings are shorter then  $t_{dip}$  the spike will be ignored (see Fig.8). The delay  $t_{dip}$  is typical 50 ms long, analog implemented and a compromise between precision and current consumption.

After an Early Warning interrupt the microcontroller should terminate any processing as fast as possible and prepare for the reset. The Early Warning interrupt flag cannot be cleared by software, it will be cleared by hardware when  $V_{DD}$  rises above the PORH level before the interrupt is served. A reset will also clear the interrupt flag by hardware.

Only for slow falling  $V_{DD}$  there is enough time to serve the interrupt. For fast falling  $V_{DD}$  the circuit will go hardware controlled into the reset state.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2.2.2 Watchdog Timer reset

If the Watchdog Timer expires, it will trigger a reset.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2.2.3 External reset via RST

An external device can cause a chip reset, if the reset pin  $\overline{\text{RST}}$  is pulled to ground.

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2.3 IDLE AND POWER-DOWN OPERATION

Idle and Power-down are power saving modes of the microcontroller that can be activated when no CPU activity is required. These two modes are extremely useful for the asynchronous CPU, because they offer the possibility to profit from the speed of the CPU and to save power as soon as the task is finished. Idle mode stops the code execution of the CPU, but the internal oscillator remains active, and also all peripheral functions connected to the on-chip clock signal. Unused blocks can be switched off independently. However, during Power-down mode the clock oscillator is stopped and therefore also all peripheral blocks will stop their activity.

#### 6.2.3.1 Idle mode

The following functions remain active during Idle mode:

- Timer 0, Timer 1 and Timer 2

- · Wake-up counter

- · Watchdog Timer counter

- MSK modem

- ADC/DAC

- POR

- I2C-bus interface

- External interrupt

- · Key pad interrupt.

The instruction that sets PCON.0 (PCON SFR) is the last instruction executed in the normal operating mode before the Idle mode is activated. The RAM and all of the registers are preserved and maintain their data during Idle mode: the CPU status, the Stack Pointer, Program Counter, Program Status Word and Accumulator.

There are two ways to terminate the Idle mode:

- Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware thus terminating the Idle mode. The interrupt is serviced, and following the RETI instruction, the next instruction to be executed will be the one following the instruction that put the device in the Idle mode.

- The second way of terminating the Idle mode is with an internal or external hardware reset. Reset redefines all SFRs but does not affect the on-chip RAM. Possible sources of an internal reset in Idle mode are:

- Watchdog Timer reset if the watchdog had expired

- POR.

#### 6.2.3.2 Power-down mode

The instruction that sets PCON.1 (PCON SFR) is the last instruction executed in the normal operating mode before the Power-down mode is activated. During Power-down mode, the RAM and all of the registers maintain their data: the CPU status, the Stack Pointer, Program Counter, Program Status Word and Accumulator.

There are two ways to terminate the Power-down mode:

- Activation of any of the below listed interrupts will cause PCON.1 to be cleared by hardware thus terminating the Power-down mode. The interrupt is serviced, and following the RETI instruction, the next instruction to be executed will be the one following the instruction that put the device in the Power-down mode. Interrupts which can generate a wake-up from power-down:

- External interrupts (INT0 to INT9)

- Timer 0 and Timer 1: only when pins T0 and T1 are used as the external timer source input (SYSCON SFR bit 7 to 4)

- Low-voltage detection interrupt

- Key pad interrupt.

- The second way of terminating the Power-down mode is with an internal or external hardware reset. Reset does not affect the on-chip RAM, but all SFRs are set to the default value. Possible source of an internal reset in power-down is: POR.

2002 Apr 24

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.2.3.3 Power Control Register (PCON)

The reduced power modes are activated by software using this Special Function Register. PCON is not bit addressable.

**Table 10** Power Control Register (SFR address 87H; reset value = 0000 0000) Bits PCON[7:2] are reserved and must be kept to logic 0.

| 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0   |

|---|---|---|---|---|---|----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | PD | IDL |

Table 11 Reduced power modes selection

| PD | IDL | DESCRIPTION                   |  |  |  |

|----|-----|-------------------------------|--|--|--|

| 0  | 0   | CPU running                   |  |  |  |

| 0  | 1   | activates the Idle mode       |  |  |  |

| 1  | 0   | activates the Power-down mode |  |  |  |

| 1  | 1   |                               |  |  |  |

#### 6.2.4 CPU START-UP TIMING

#### 6.2.4.1 CPU start-up after reset

Three possibilities how the CPU can start executing code after a reset phase are described below.

When the CPU is triggered to wake-up after a power-on reset (see Fig.9), the clock oscillator usually needs some time to ramp up. To allow the oscillator to stabilize the CPU contains a down counter for a fixed delay of 1024 + 16 clock cycles. After this delay the CPU starts with code execution.

When CPU start-up is initiated from an external reset (see Fig.11), the down counter is not initialized and the time between reset going active and first code execution can be maximum 16400 clock cycles.

When a CPU start-up is after a Watchdog Timer reset (see Fig.10), the RST pin will be pulled low for 1024 clock cycles. Another 16 clocks later the CPU will start executing code.

#### 6.2.4.2 CPU start-up after power-down

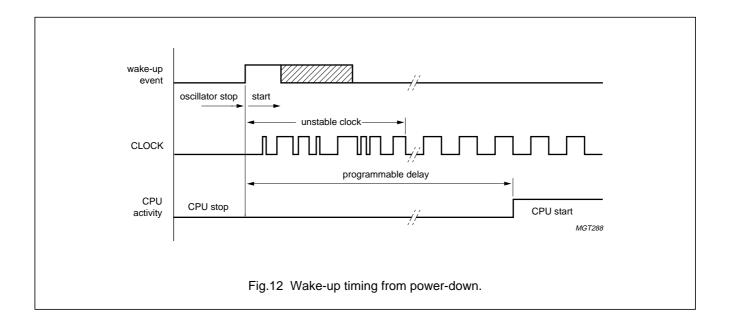

After wake-up from Power-down mode (see Fig.12) the user has the possibility to shorten the start-up time by programming the Wake-up Counter Register (WKCON). This can be useful when an external clock source is used instead of the on-chip oscillator, or when the accuracy of the time reference is not needed immediately after a restart. This feature enables power saving and fast wake-up in applications where the CPU frequently goes in Power-down mode. The wake-up delay can be calculated as shown in Table 13.

Table 12 Wake-up Counter Register (WKCON; SFR address DDH)

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WKCON.7 | WKCON.6 | WKCON.5 | WKCON.4 | WKCON.3 | WKCON.2 | WKCON.1 | WKCON.0 |

Table 13 Description of WKCON bits

| BIT    | SYMBOL      | DESCRIPTION                                                                                                                                                                                                                                                                         |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 | WKCON.[7:0] | The wake-up delay can be calculated as follows:  Wake-up delay = 1024 - 4 × WKCON  Where WKCON is the content of the Wake-up Counter Register.  WKCON = 00H: (default) wake-up delay = 1024 clocks  WKCON = CCH: wake-up delay = 208 clocks  WKCON = FFH: wake-up delay = 4 clocks. |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3 Interrupt controller

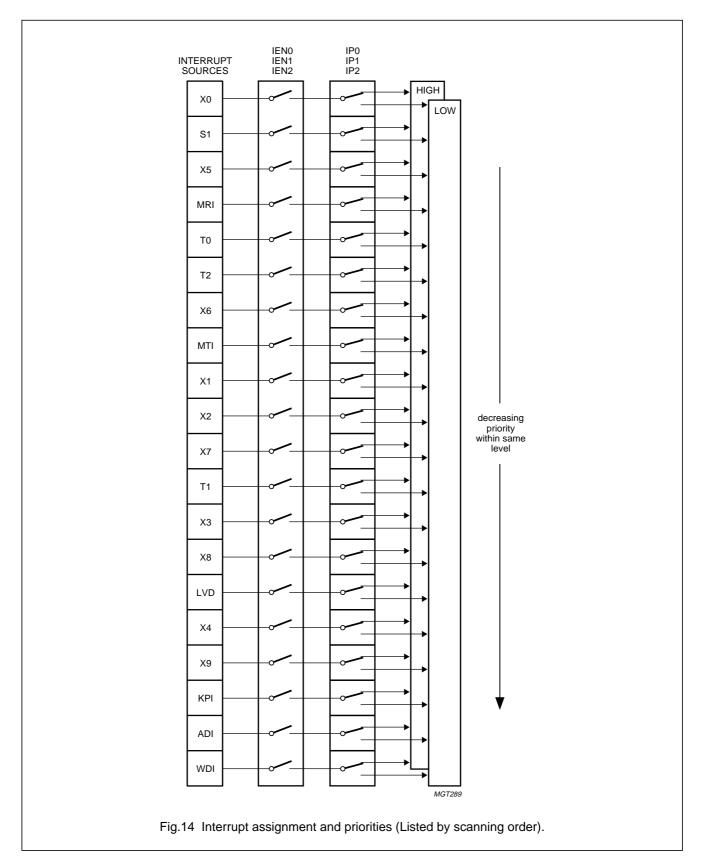

In order to service interrupt requests coming from external events and from the on-chip peripherals the P87CL888 offers a 20 source, two priority level nested interrupt system. A detailed description of the interrupt process is given in the following sections. Table 14 shows the available interrupts with each vector address and Table 15 shows an overview of all the interrupt related SFRs. The detailed interrupt related SFR description can be found in Sections 6.3.4 to 6.3.10.

#### 6.3.1 GENERAL

Each interrupt vector points to a separate location in program memory for its service routine. Each source can be individually enabled or disabled by its corresponding bit in the Interrupt Enable Registers (IEN0, IEN1 and IEN2). The priority level is selected via the Interrupt Priority Registers (IP0, IP1 and IP2). All available interrupts can be globally disabled or enabled.

The interrupt controller samples all active sources during one instruction cycle. Evaluation of the interrupts is then performed. A priority decoder decides which interrupt is serviced. Each interrupt has its own vector pointing to an 8 bytes long memory segment.

A low priority interrupt can be interrupted by a high priority interrupt, but not by another low priority interrupt i.e. only two interrupt levels are possible.

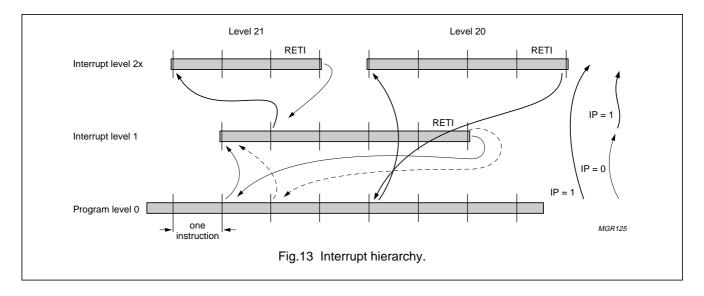

Between the RETI instruction (Return from Interrupt) and the execution of a next interrupt at least one instruction of the lower program level is executed. The interrupt service with different priorities is shown in Fig.13.

An interrupt is performed with a long subroutine call (LCALL) to a vector address, which is determined by the respective interrupt. During LCALL the Program Counter (PC) is pushed onto the stack. Returning from interrupt with RETI, the PC is popped from the stack.

In the event of several interrupts with the same priority level, the order of sequence in which they will be serviced is determined by the scanning order.

The interrupt highest in the scanning list will always be served first, interrupts lower in the scanning list will be served in the order as shown in Fig.14. No interrupt will be lost.

**Table 14** Available interrupts (ordered by vector address) HW = hardware; SW = software.

| SOURCE                               | SYMBOL | VECTOR<br>(HEX) | CLEARED<br>BY |

|--------------------------------------|--------|-----------------|---------------|

| INT 0                                | X0     | 0003            | HW            |

| Timer 0                              | T0     | 000B            | HW            |

| INT 1                                | X1     | 0013            | HW            |

| Timer 1                              | T1     | 001B            | HW            |

| I <sup>2</sup> C-bus                 | S1     | 002B            | SW            |

| Timer 2                              | T2     | 0033            | SW            |

| INT2                                 | X2     | 003B            | SW            |

| INT3                                 | Х3     | 0043            | SW            |

| INT4                                 | X4     | 004B            | SW            |

| INT5                                 | X5     | 0053            | SW            |

| INT6                                 | X6     | 005B            | SW            |

| INT7                                 | X7     | 0063            | SW            |

| INT8                                 | X8     | 006B            | SW            |

| INT9                                 | X9     | 0073            | SW            |

| MSK modem transmitter                | MTI    | 0083            | SW            |

| MSK mode receiver                    | MRI    | 008B            | SW            |

| Low voltage detector                 | LVD    | 0093            | HW            |

| Key pad interrupt                    | KPI    | 00A3            | SW            |

| Analog-to-Digital<br>Converter (ADC) | ADI    | 00AB            | SW            |

| Watchdog Timer                       | WDI    | 00B3            | SW            |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

Table 15 Interrupt related SFRs

| SFR  | DESCRIPTION                                  | SFR ADDRESS | RESET VALUE |

|------|----------------------------------------------|-------------|-------------|

| IEN0 | Interrupt Enable Register 0                  | A8H         | 0000 0000   |

| IEN1 | Interrupt Enable Register 1 (INT2 to INT9)   | E8H         | 0000 0000   |

| IEN2 | Interrupt Enable Register 2                  | F1H         | 0000 0000   |

| IP0  | Interrupt Priority Register 0                | B8H         | 0000 0000   |

| IP1  | Interrupt Priority Register 1 (INT2 to INT9) | F8H         | 0000 0000   |

| IP2  | Interrupt Priority Register 2                | F9H         | 0000 0000   |

| IX1  | External Interrupt Polarity Register 1       | E9H         | 0000 0000   |

| ISE1 | External Interrupt Sensitivity Register 1    | E1H         | 0000 0000   |

| IRQ1 | External Interrupt Request Flag Register 1   | C0H         | 0000 0000   |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.2 INTERRUPT PROCESS

- 1. **Sample the interrupt lines.** The interrupt lines are latched at the beginning of each instruction cycle.

- 2. Analyse the requests. The sampled interrupt lines will be analysed with respect to the relevant Interrupt Enable Register (IENx) and Interrupt Priority Register (IPx). The process will deliver the vector of the highest interrupt request and the priority information. Depending on the interrupt level and the priority of the interrupt in progress, an interrupt request to the core is performed. The vector address will be passed to the core process.

#### 3. Interrupt request to core.

- a) Level 0: the interrupt request to the core is performed, when at least one instruction is performed since the RETI from Level 1.

- b) Level 1: the interrupt request is performed, when at least one instruction is performed since the RETI from Level 21 and the request has high priority.

- c) Level 20: no request is performed.

- d) Level 21: no request is performed.

#### 4. Update the interrupt level.

- a) Level 0: in the event of a high priority interrupt the new level will be Level 20; if it is a low priority interrupt, the new level will be Level 1.

- b) Level 1: in the event of a high priority interrupt, the new level will be Level 21; a low priority interrupt is not performed, the level is unchanged; on RETI the new level will be Level 0.

- c) Level 20: on RETI; the new level is Level 0.

- d) Level 21: on RETI; the new level is Level 1.

- e) Level 1: on RETI; the new level is Level 0.

- f) Level 0: the new level is Level 0.

- Clearing the flags. During the forced LCALL the interrupt flag of the relevant interrupt is cleared by hardware, if applicable, otherwise by software.

- 6. Idle and power-down. When Idle (PCON.0) or Power-down (PCON.1) is set, the interrupt controller waits for the according wake-up signal. Because the interrupt controller is waiting for wake-up, all activity in the circuit will be stopped, thus no handshake can be completed. The wake-up signal for Idle is the OR of all the interrupt request bits and the reset. For power-down the wake-up signal is built only with the Port 1 external interrupt request flags (X2 to X9) and the reset (external reset or power-on reset).

#### 6.3.3 PORT 1 INTERRUPTS

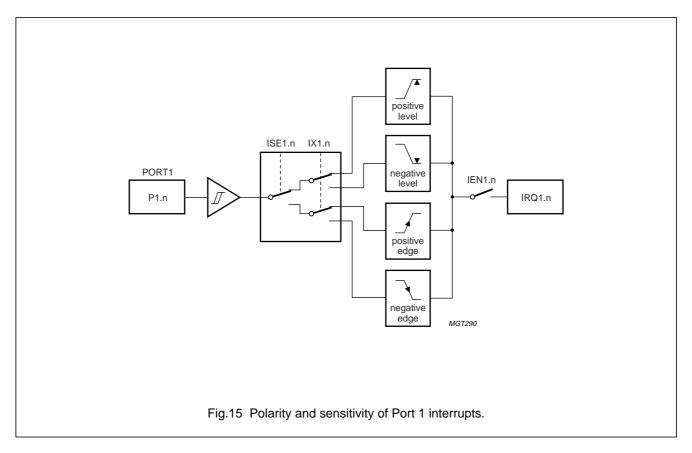

Eight Port 1 lines can be used as external interrupt inputs (X2 to X9). When enabled by IEN1 SFR, each of these interrupts may wake-up the device from Idle or Power-down. These external interrupts can each independently be programmed to positive and negative polarity and to edge and level sensitivity by setting SFR IX1 and ISE1 (see Table 34). Figure 15 shows programming of polarity and sensitivity of the Port 1 interrupts. When a valid event occurs on an enabled Port 1 interrupt, the corresponding bit in the Interrupt Request Flags Register will be set (IRQ1). The interrupt request flags must be cleared by software.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.4 INTERRUPT ENABLE REGISTER 0 (IEN0)

Table 16 Interrupt Enable Register 0 (SFR address A8H)

| 7  | 6   | 5   | 4 | 3   | 2   | 1   | 0   |

|----|-----|-----|---|-----|-----|-----|-----|

| EA | ET2 | ES1 | _ | ET1 | EX1 | ET0 | EX0 |

#### Table 17 Description of IEN0 bits

Logic 0 = interrupt disabled; logic 1 = interrupt enabled.

| BIT | SYMBOL | DESCRIPTION                                                                                                                                 |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA     | <b>General enable/disable control</b> . If EA = 0, no interrupt is enabled; if EA = 1, any individually enabled interrupt will be accepted. |

| 6   | ET2    | enable T2 interrupt                                                                                                                         |

| 5   | ES1    | enable I <sup>2</sup> C-bus interrupt                                                                                                       |

| 4   | _      | reserved                                                                                                                                    |

| 3   | ET1    | enable Timer 1 interrupt (T1)                                                                                                               |

| 2   | EX1    | enable external interrupt 1                                                                                                                 |

| 1   | ET0    | enable Timer 0 interrupt (T0)                                                                                                               |

| 0   | EX0    | enable external interrupt 0                                                                                                                 |

#### 6.3.5 INTERRUPT ENABLE REGISTER 1 (IEN1)

#### Table 18 Interrupt Enable Register 1 (SFR address E8H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| EX9 | EX8 | EX7 | EX6 | EX5 | EX4 | EX3 | EX2 |

#### Table 19 Description of IEN1 bits

Logic 0 = interrupt disabled; logic 1 = interrupt enabled.

| BIT | SYMBOL | DESCRIPTION                 |  |  |  |

|-----|--------|-----------------------------|--|--|--|

| 7   | EX9    | enable external interrupt 9 |  |  |  |

| 6   | EX8    | enable external interrupt 8 |  |  |  |

| 5   | EX7    | enable external interrupt 7 |  |  |  |

| 4   | EX6    | enable external interrupt 6 |  |  |  |

| 3   | EX5    | enable external interrupt 5 |  |  |  |

| 2   | EX4    | enable external interrupt 4 |  |  |  |

| 1   | EX3    | enable external interrupt 3 |  |  |  |

| 0   | EX2    | enable external interrupt 2 |  |  |  |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.6 INTERRUPT ENABLE REGISTER 2 (IEN2)

Table 20 Interrupt Enable Register 2 (SFR address F1H)

| 7    | 6    | 5    | 4 | 3    | 2 | 1    | 0    |

|------|------|------|---|------|---|------|------|

| EWDI | EADI | EKPI | _ | ELVD | _ | EMTI | EMRI |

#### Table 21 Description of IEN2 bits

Logic 0 = interrupt disabled; logic 1 = interrupt enabled.

| BIT | SYMBOL | DESCRIPTION                            |

|-----|--------|----------------------------------------|

| 7   | EWDI   | enable Watchdog Timer interrupt        |

| 6   | EADI   | enable ADC interrupt                   |

| 5   | EKPI   | enable key pad interrupt               |

| 4   | _      | reserved                               |

| 3   | ELVD   | enable low-voltage detector interrupts |

| 2   | _      | reserved                               |

| 1   | EMTI   | enable MSK transmitter interrupt       |

| 0   | EMRI   | enable MSK receiver interrupts         |

#### 6.3.7 INTERRUPT PRIORITY REGISTER 0 (IP0)

#### Table 22 Interrupt Priority Register 0 (SFR address B8H)

| 7 | 6   | 5   | 4 | 3   | 2   | 1   | 0   |

|---|-----|-----|---|-----|-----|-----|-----|

| _ | PT2 | PS1 | - | PT1 | PX1 | PT0 | PX0 |

#### Table 23 Description of IP0 bits

Logic 0 = low priority; logic <math>1 = high priority.

| BIT | SYMBOL | DESCRIPTION                                   |  |  |  |

|-----|--------|-----------------------------------------------|--|--|--|

| 7   | _      | reserved                                      |  |  |  |

| 6   | PT2    | Timer 2 interrupt priority level              |  |  |  |

| 5   | PS1    | I <sup>2</sup> C-bus interrupt priority level |  |  |  |

| 4   | _      | reserved                                      |  |  |  |

| 3   | PT1    | Timer 1 interrupt priority level              |  |  |  |

| 2   | PX1    | external interrupt 1 priority level           |  |  |  |

| 1   | PT0    | Timer 0 interrupt priority level              |  |  |  |

| 0   | PX0    | external interrupt 0 priority level           |  |  |  |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.8 INTERRUPT PRIORITY REGISTER 1 (IP1)

Table 24 Interrupt Priority Register 1 (SFR address F8H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PX9 | PX8 | PX7 | PX6 | PX5 | PX4 | PX3 | PX2 |

#### Table 25 Description of IP1 bits

Logic 0 = low priority; logic <math>1 = high priority.

| BIT | SYMBOL | DESCRIPTION                         |

|-----|--------|-------------------------------------|

| 7   | PX9    | external interrupt 9 priority level |

| 6   | PX8    | external interrupt 8 priority level |

| 5   | PX7    | external interrupt 7 priority level |

| 4   | PX6    | external interrupt 6 priority level |

| 3   | PX5    | external interrupt 5 priority level |

| 2   | PX4    | external interrupt 4 priority level |

| 1   | PX3    | external interrupt 3 priority level |

| 0   | PX2    | external interrupt 2 priority level |

#### 6.3.9 INTERRUPT PRIORITY REGISTER 2 (IP2)

#### Table 26 Interrupt Priority Register 2 (SFR address F9H)

| 7    | 6    | 5    | 4 | 3    | 2 | 1    | 0    |

|------|------|------|---|------|---|------|------|

| PWDI | PADI | PKPI | _ | PLVD | _ | PMTI | PMRI |

#### Table 27 Description of IP2 bits

Logic 0 = low priority; logic <math>1 = high priority.

| BIT | SYMBOL | DESCRIPTION                                  |  |  |  |

|-----|--------|----------------------------------------------|--|--|--|

| 7   | PWDI   | Watchdog Timer interrupt priority level      |  |  |  |

| 6   | PADI   | ADC interrupt priority level                 |  |  |  |

| 5   | PKPI   | key pad interrupt priority level             |  |  |  |

| 4   | _      | eserved                                      |  |  |  |

| 3   | PLVD   | w-voltage detection interrupt priority level |  |  |  |

| 2   | _      | reserved                                     |  |  |  |

| 1   | PMTI   | MSK transmitter interrupt priority level     |  |  |  |

| 0   | PMRI   | MSK receiver interrupt priority level        |  |  |  |

## 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.10 INTERRUPT REQUEST FLAG REGISTER 1 (IRQ1)

Table 28 Interrupt Request Flag Register 1 (SFR address C0H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IQ9 | IQ8 | IQ7 | IQ6 | IQ5 | IQ4 | IQ3 | IQ2 |

Table 29 Description of IRQ1 bits

| BIT | SYMBOL | DESCRIPTION                       |

|-----|--------|-----------------------------------|

| 7   | IQ9    | external interrupt 9 request flag |

| 6   | IQ8    | external interrupt 8 request flag |

| 5   | IQ7    | external interrupt 7 request flag |

| 4   | IQ6    | external interrupt 6 request flag |

| 3   | IQ5    | external interrupt 5 request flag |

| 2   | IQ4    | external interrupt 4 request flag |

| 1   | IQ3    | external interrupt 3 request flag |

| 0   | IQ2    | external interrupt 2 request flag |

#### 6.3.11 INTERRUPT POLARITY AND SENSITIVITY REGISTERS

#### 6.3.11.1 Interrupt Polarity Register 1 (IX1)

Writing either a logic 1 or logic 0 to any Interrupt Polarity Register bit sets the polarity of the corresponding external interrupt. If the interrupt sensitivity bit (ISE1 register, Section 6.3.11.2) is set to 'level' sensitive then a logic 1 corresponds to active HIGH level and logic 0 to active LOW level. If the ISE1 register is set to 'edge' sensitive then a logic 1 corresponds to a rising edge and a logic 0 to a falling edge. See also Table 34 and Fig.15.

Table 30 Interrupt Polarity Register 1 (SFR address E9H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IX9 | IX8 | IX7 | IX6 | IX5 | IX4 | IX3 | IX2 |

Table 31 Description of IX1 bits

| BIT    | SYMBOL     | DESCRIPTION                              |  |

|--------|------------|------------------------------------------|--|

| 7 to 0 | IX9 to IX2 | external interrupt 9 to 2 polarity level |  |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.3.11.2 Interrupt Sensitivity Register 1 (ISE1)

Writing either a logic 1 or logic 0 to an Interrupt Sensitivity Register bit sets the type of the corresponding external interrupt to edge sensitive (logic 1) or level sensitive (logic 0) respectively.

Table 32 Interrupt Sensitivity Register 1 (SFR address E1H)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| ISE9 | ISE8 | ISE7 | ISE6 | ISE5 | ISE4 | ISE3 | ISE2 |

Table 33 Description of ISE1 bits

| BIT    | SYMBOL       | DESCRIPTION                           |

|--------|--------------|---------------------------------------|

| 7 to 0 | ISE9 to ISE2 | external interrupt 9 to 2 sensitivity |

#### 6.3.11.3 Interrupt polarity and sensitivity options

**Table 34** Interrupt polarity and sensitivity options 'n' denotes the bit position in the SFRs IX1 and ISE1.

| IX1.n | ISE1.n | DESCRIPTION            |  |  |  |

|-------|--------|------------------------|--|--|--|

| 0     | 0      | LOW-level sensitive    |  |  |  |

| 1     | 0      | HIGH-level sensitive   |  |  |  |

| 0     | 1      | falling edge sensitive |  |  |  |

| 1     | 1      | rising edge sensitive  |  |  |  |

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

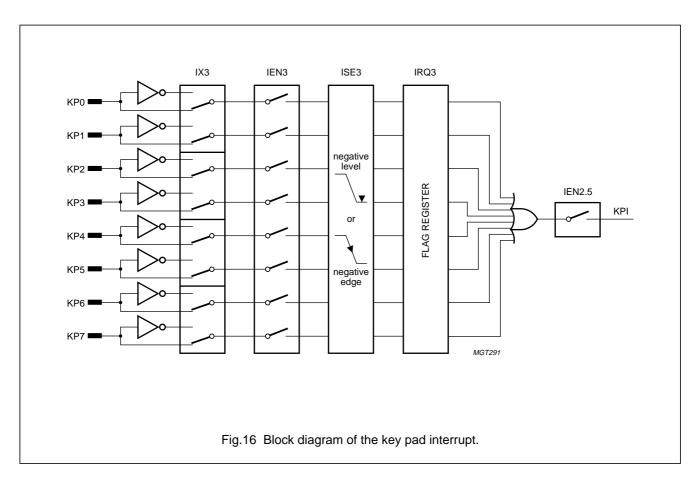

#### 6.4 Key Pad Interrupt (KPI)

The key pad interrupt is a logical 'OR' of 8 inputs from Port 4 (KP0 to KP7). The key pad interrupt generates only 1 interrupt source to the interrupt controller (KPI).

A key pad interrupt is implemented to read out a key board with 8 interrupt lines. An event on one of the inputs KP0 to KP7 generates a KPI interrupt. Each of the key pad interrupt inputs can individually be enabled by setting the corresponding bit in the IEN3 register. The key pad interrupt can be globally disabled by writing to IEN2.5 in the interrupt controller. Each pin can be initialized to both polarities depending on the settings in the Interrupt Polarity Register 3 (IX3). The key pad interrupt can be made edge or level sensitive by writing to the ISE3 register. See Table 44.

The key pad interrupts are set by hardware and must be cleared by software. Table 35 gives an overview of the key pad interrupt related registers. Sections 6.4.3.1 to 6.4.3.2 give detailed description of the SFRs.

Table 35 Key Pad Interrupt related SFRs

| ADDR | SFR  | DESCRIPTION                                  |

|------|------|----------------------------------------------|

| F4H  | IX3  | Key Pad Interrupt Polarity Register 3        |

| F5H  | IRQ3 | Key Pad Interrupt Request Flag<br>Register 3 |

| F6H  | IEN3 | Key Pad Interrupt Enable Register 3          |

| F7H  | ISE3 | Key Pad Interrupt Sensitivity Register 3     |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.4.1 KEY PAD INTERRUPT REQUEST FLAG REGISTER 3 (IRQ3)

Table 36 Key Pad Interrupt Request Flag Register 3 (SFR address F5H)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IQKP7 | IQKP6 | IQKP5 | IQKP4 | IQKP3 | IQKP2 | IQKP1 | IQKP0 |

#### Table 37 Description of IRQ3 bits

| BIT | SYMBOL | DESCRIPTION                      |  |  |  |

|-----|--------|----------------------------------|--|--|--|

| 7   | IQKP7  | key pad interrupt 7 request flag |  |  |  |

| 6   | IQKP6  | key pad interrupt 6 request flag |  |  |  |

| 5   | IQKP5  | key pad interrupt 5 request flag |  |  |  |

| 4   | IQKP4  | key pad interrupt 4 request flag |  |  |  |

| 3   | IQKP3  | key pad interrupt 3 request flag |  |  |  |

| 2   | IQKP2  | key pad interrupt 2 request flag |  |  |  |

| 1   | IQKP1  | key pad interrupt 1 request flag |  |  |  |

| 0   | IQKP0  | key pad interrupt 0 request flag |  |  |  |

#### 6.4.2 KEY PAD INTERRUPT ENABLE REGISTER 3 (IEN3)

#### Table 38 Key Pad Interrupt Enable Register 3 (SFR address F6H)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| EKP7 | EKP6 | EKP5 | EKP4 | EKP3 | EKP2 | EKP1 | EKP0 |

#### Table 39 Description of IEN3 bits

Logic 0 = interrupt disabled; logic 1 = interrupt enabled.

| BIT | SYMBOL | DESCRIPTION                  |

|-----|--------|------------------------------|

| 7   | EKP7   | enable key pad interrupt KP7 |

| 6   | EKP6   | enable key pad interrupt KP6 |

| 5   | EKP5   | enable key pad interrupt KP5 |

| 4   | EKP4   | enable key pad interrupt KP4 |

| 3   | EKP3   | enable key pad interrupt KP3 |

| 2   | EKP2   | enable key pad interrupt KP2 |

| 1   | EKP1   | enable key pad interrupt KP1 |

| 0   | EKP0   | enable key pad interrupt KP0 |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.4.3 KEY PAD INTERRUPT POLARITY AND SENSITIVITY REGISTERS

#### 6.4.3.1 Key Pad Interrupt Polarity Register 3 (IX3)

Writing either a logic 1 or logic 0 to any Key pad Interrupt Polarity Register bit sets the polarity level of the corresponding external key pad interrupt to an active HIGH (rising edge) or active LOW (falling edge) respectively. See also Table 44 and Fig.16

Table 40 Key Pad Interrupt Polarity Register 3 (SFR address F4H)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IXKP7 | IXKP6 | IXKP5 | IXKP4 | IXKP3 | IXKP2 | IXKP1 | IXKP0 |

Table 41 Description of IX3 bits

| BIT    | SYMBOL         | DESCRIPTION                             |

|--------|----------------|-----------------------------------------|

| 7 to 0 | IXKP7 to IXKP0 | key pad interrupt 7 to 0 polarity level |

#### 6.4.3.2 Key Pad Interrupt Sensitivity Register 3 (ISE3)

Writing either a logic 1 or logic 0 to any Key Pad Interrupt Sensitivity Register bit sets the type of the corresponding external interrupt to edge sensitive or level sensitive respectively.

Table 42 Key Pad Interrupt Sensitivity Register (SFR address F7H)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ISKP7 | ISKP6 | ISKP5 | ISKP4 | ISKP3 | ISKP2 | ISKP1 | ISKP0 |

Table 43 Description of ISE3 bits

| BIT    | SYMBOL         | DESCRIPTION                          |

|--------|----------------|--------------------------------------|

| 7 to 0 | ISKP7 to ISKP0 | key pad interrupt 7 to 0 sensitivity |

#### 6.4.3.3 Key pad interrupt level and sensitivity selection

#### Table 44 Key pad interrupt options

'n' denotes the bit position in the SFRs IX3 and ISE3.

| IX3.n | ISE3.n | DESCRIPTION            |  |  |

|-------|--------|------------------------|--|--|

| 0     | 0      | LOW-level sensitive    |  |  |

| 1     | 0      | HIGH-level sensitive   |  |  |

| 0     | 1      | falling edge sensitive |  |  |

| 1     | 1      | rising edge sensitive  |  |  |

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.5 Port control logic

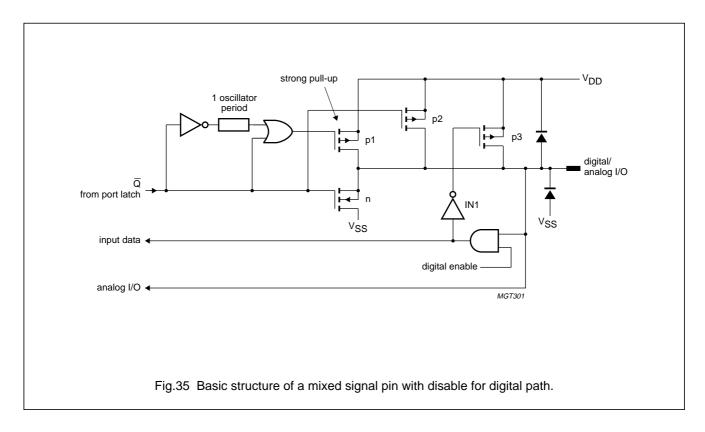

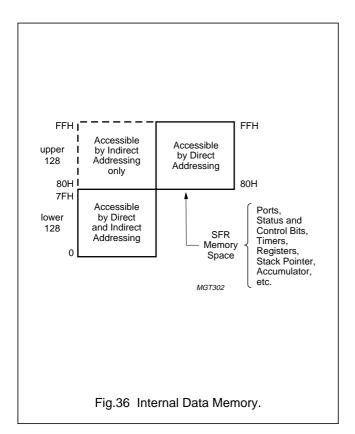

Four 8-bit I/O ports are implemented in the device. Some of these general purpose I/Os are multiplexed with alternative functions. Port 0 is the only port with no multiplexed alternative functions. Port 3 and a part of Port 1 are multiplexed with analog functions. Every port bit can be independently configured in 4 different modes.

#### 6.5.1 PORT FUNCTIONALITY

Port 0 8-bit bidirectional I/O port with no alternative functions. Every port pin can be used as open-drain, standard port, high-impedance input or push-pull output. Port 0 is used during emulation mode.

Port 1 8-bit bidirectional I/O port with alternative functions. Every port, except P1.6 and P1.7 can be used as open-drain, standard port, high-impedance input or push-pull output.

- P1.0 to P1.7 provides the inputs for the external interrupts INT2 to INT9; the interrupts are enabled by selecting the proper bit in the interrupts enable register

- P1.0 to P1.2 provides the analog inputs ADC5 to ADC3<sup>(1)</sup>; the port must be set in the high-impedance configuration to enable the analog input function

- P1.1 and P1.2 provide the Timer 2 external trigger input (T2EX) and the Timer 2 external count input (T2)

- P1.4 provides the clock output CLKOUT (f<sub>psc</sub> or f<sub>per</sub>)

- P1.5 provide the Timer 2 clock output of the clock-output mode (T2OUT); to enable output the data SFR must contain logic 1s

- P1.6 and P1.7 provide the I<sup>2</sup>C-bus clock and data I/O, SCL and SDA. P1.6 and P1.7 can only be configured as open-drain output or high-impedance input; there is no clamp diode to V<sub>DD</sub>. I<sup>2</sup>C-bus signals are connected to the port if bit ENS1 (S1CON SFR) is set to logic 1.

#### Port 2 Not used.

The ports which have an analog option (e.g.: ADCn and DACn) multiplexed do not have a hysteresis input. Port 3 8-bit bidirectional I/O port with alternative functions. Every port can be used as open-drain, standard port, high-impedance input or push-pull output.

- P3.0 to P3.2 provide the MSK output signals MOUT0, MOUT1 and MOUT2

- P3.3 and P3.4 provide the DAC0 and DAC1<sup>(1)</sup> analog output; the port must be set in the high-impedance configuration to enable the analog output function

- P3.4 also provides the Timer 0 external clock input

- P3.5 to P3.7 provide the ADC0 till ADC2<sup>(1)</sup>

analog input; the port must be set in the

high-impedance configuration to enable the

analog input function

- P3.5 also provides the Timer 1 external clock input.

Port 4 8-bit bidirectional I/O port with alternative functions. Every port pin can be used as open-drain, standard port, high-impedance input or push-pull output.

> P4.0 to P4.7 provides the key pad interrupt functionality KP0 to KP7; the keypad interrupt lines are enabled by setting a value in the Key Pad Interrupt Enable Register 3 (IEN3).

### 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.5.2 PORT I/O CONFIGURATION

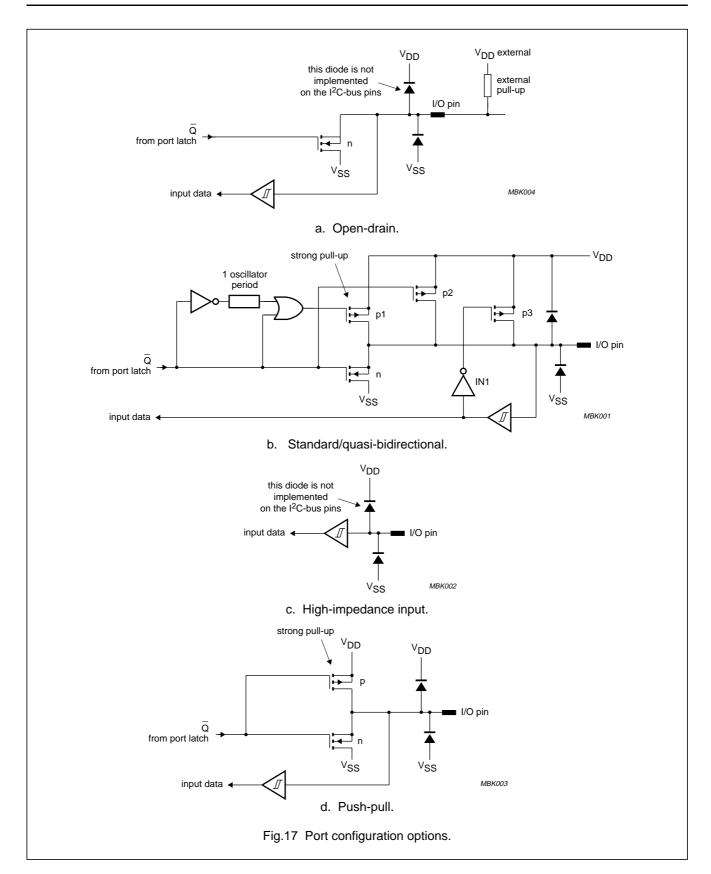

Each port bit consist of a data latch, two configuration latches, an output driver and an input buffer. The I/O port configurations are determined by the settings in the port configuration SFRs, PnCFGA and PnCFGB, where 'n' indicates the specific port number (0, 1, 3 and 4). The combination of 2 bits in each of the 2 configuration SFRs relates to the output setting for the corresponding port pin, allowing any combination of the 4 I/O modes to be mixed on those port pins. The port I/O configuration types are shown in Fig.17 and described in Sections 6.5.2.1 to 6.5.2.4.

#### 6.5.2.1 Open-drain

Quasi-bidirectional I/O with n-channel open-drain output. Use as an output requires the connection of an external pull-up resistor; all pins have ESD protection diodes against  $V_{DD}$  and  $V_{SS}$ , except for the I<sup>2</sup>C-bus pins P1.6 and P1.7, which have no ESD protection to  $V_{DD}$ .

#### 6.5.2.2 Standard port

Quasi-bidirectional I/O with pull-up; the strong pull-up 'p1' is turned on for three clock ( $f_{osc}$ ) edges after a LOW-to-HIGH transition in the port latch; after these three clock edges the port is only weakly driven through 'p2' and 'very weakly' driven through 'p3' (see Fig.17b).

#### 6.5.2.3 High-impedance input

This mode turns off all output drivers on a port. The pin will not source or sink current and may be used as an input-only pin. (see Fig.17c). In order not to increase the current consumption the high-impedance input should not float.

#### 6.5.2.4 Push-pull

Output with drive capability in both polarities; under this mode, pins can only be used as outputs (see Fig.17d).

**Table 45** Port I/O configuration types 'n' indicates the specific port number (0, 1, 3 and 4).

| TYPE                 | PnCFGA | PnCFGB | NORMAL PORTS         | I <sup>2</sup> C-BUS PORTS |

|----------------------|--------|--------|----------------------|----------------------------|

| Open-drain           | 0      | 0      | open-drain           | open-drain                 |

| Standard port        | 1      | 0      | quasi-bidirectional  | open-drain                 |

| High-impedance input | 0      | 1      | high-impedance input | high-impedance input       |

| Push-pull            | 1      | 1      | push-pull            | open-drain                 |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

Table 46 Reset state of port related SFRs

| SFR    | DESCRIPTION            | SFR ADDRESS<br>(HEX) | STATE AFTER RESET <sup>(1)</sup> |

|--------|------------------------|----------------------|----------------------------------|

| P0     | Port 0 output data     | 80                   | 1110 1111                        |

| P0CFGA | Port 0 Configuration A | 8E                   | 1111 0011                        |

| P0CFGB | Port 0 Configuration B | 8F                   | 0000 0000                        |

| P1     | Port 1 output data     | 90                   | 1111 1111                        |

| P1CFGA | Port 1 Configuration A | 9E                   | 1111 1111                        |

| P1CFGB | Port 1 Configuration B | 9F                   | 0000 0000                        |

| P3     | Port 3 output data     | В0                   | 1111 1111                        |

| P3CFGA | Port 3 Configuration A | BE                   | 1111 1111                        |

| P3CFGB | Port 3 Configuration B | BF                   | 0000 0000                        |

| P4     | Port 4 output data     | C1                   | 1111 1110                        |

| P4CFGA | Port 4 Configuration A | CE                   | 1111 1111                        |

| P4CFGB | Port 4 Configuration B | CF                   | 0000 0000                        |

#### Note

1. This means all ports, except P0.2, P0.3, P0.4, P1.6, P1.7 and P4.0 are initialized in standard port configuration driving a weak logic 1. Port 0.2 and P0.3 are initialised as open-drain outputs, floating. P0.4 is initialised as bidirectional, driving a strong logic 0. I<sup>2</sup>C-bus I/Os P1.6 and P1.7 are initialised in open-drain configuration, floating. The configuration registers (P1CFGA.7 to 6 and P1CGB.7 to 6) are however configured as standard port configuration but the connections to the port PMOS transistors are not present. P4.0 is initialised as bidirectional, driving a strong logic 0.

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

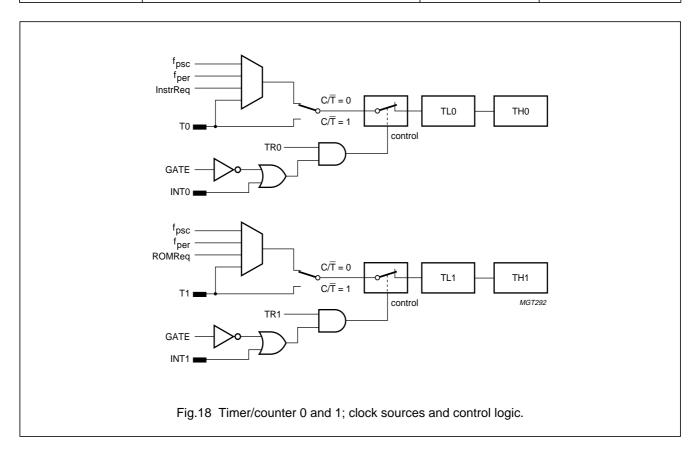

#### 6.6 Timer 0 and Timer 1 event counters

Timer 0 and Timer 1 can perform the following functions:

- · Measure time intervals and pulse durations

- · Count events

- Measure CPU speed

- Generate interrupt requests.

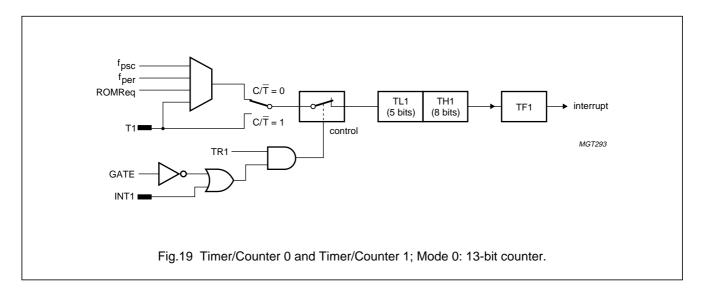

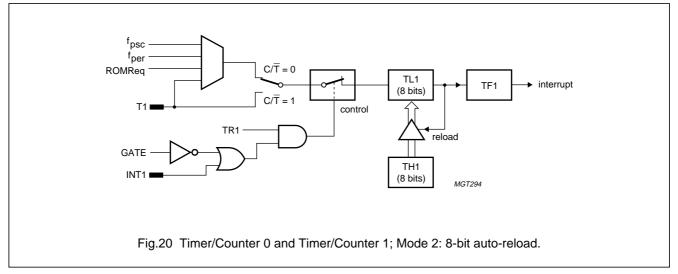

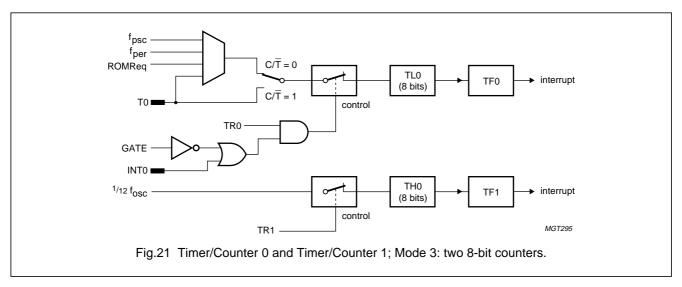

Timer 0 and Timer 1 can be programmed independently to operate in four modes:

- Mode 0 8-bit timer or 8-bit counter each with divide-by-32 prescaler.

- Mode 1 16-bit time interval or event counter.

- Mode 2 8-bit time interval or event counter with automatic reload upon overflow.

- Mode 3 Timer 1 stopped and Timer 0 operates as two separate counters.

A block diagram of Timer 0 and Timer 1 with possible clock sources is shown in Fig.18.

Table 47 Timer/Counter 0 and 1 related SFRs

| SFR    | DESCRIPTION                                 | SFR ADDRESS | RESET VALUE |

|--------|---------------------------------------------|-------------|-------------|

| TCON   | Timer/counter 0 and 1 Control Register      | 88H         | 0000 0000   |

| TMOD   | Timer/counter 0 and 1 Mode Control Register | 89H         | 0000 0000   |

| SYSCON | System Control Register                     | B4H         | 0000 0000   |

# 80C51 Ultra Low Power (ULP) telephony controller

P87CL888

#### 6.6.1 CLOCK SOURCE SIGNALS OF TIMER 0 AND TIMER 1

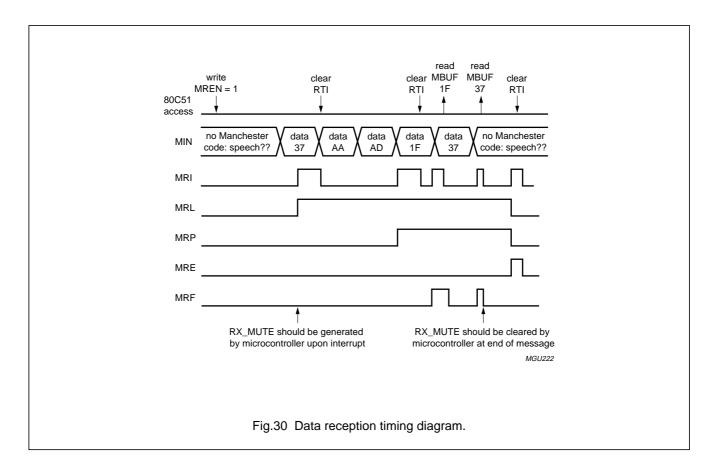

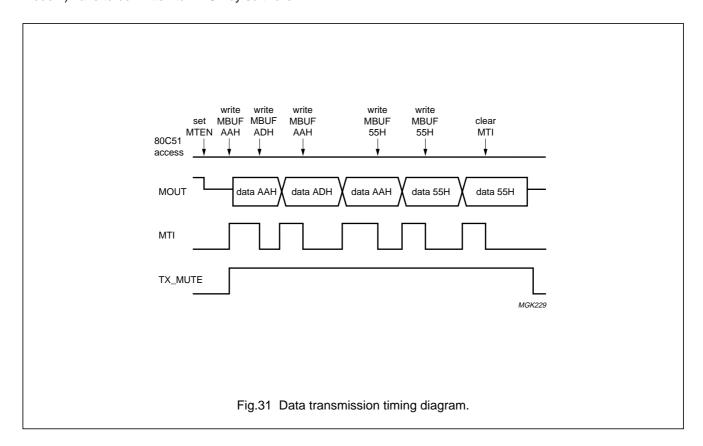

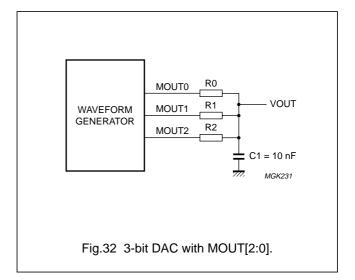

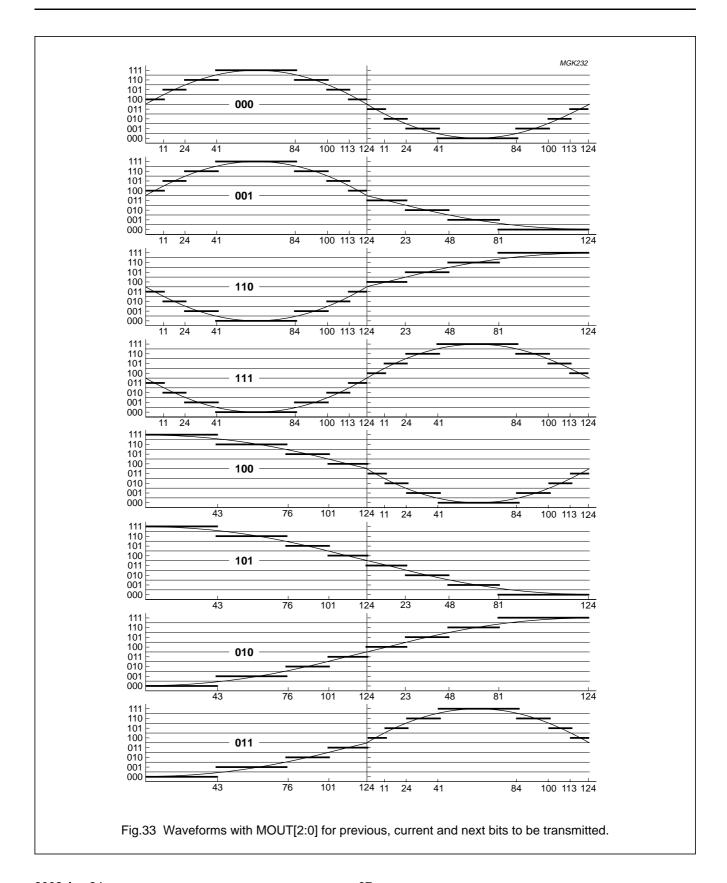

In all four modes Timer 0 and Timer 1 can be configured to increment from different internal and external clock sources. The TMOD and SYSCON registers must be written to determine the source of the clock signal. After reset the clock source for both timers is connected to the internal clock signal from PSC1 ( $f_{psc}$ ). The second of four possible clock sources is connected to the other internal clock signal coming from PSC2 ( $f_{per}$ ).